# 技術情報 TECHNICAL INFORMATION

# スイッチングタイム測定/Switching Time Test

### 1. 負荷抵抗スイッチング測定

Load resistance switching measurement

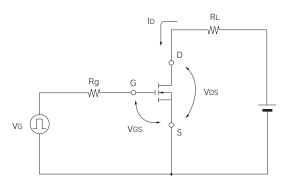

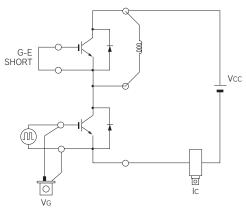

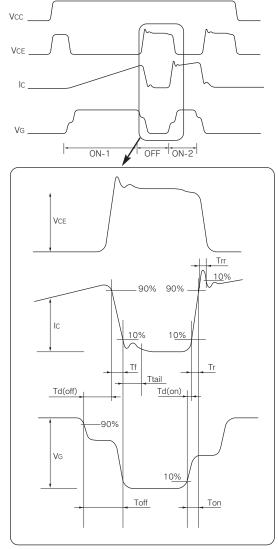

fig-1とfig-2にR負荷スイッチング時の基本測定回路と各部の電圧、 電流波形を示す。

Fig-1 and 2 indicate the fundamental measurement circuit and the waveform for each units voltage and current, during the R-load swithing.

fig-1 RL負荷スイッチング基本測定回路

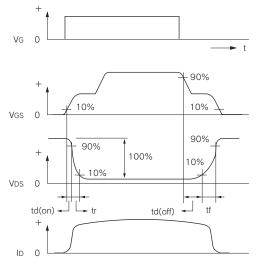

fig-2 RL負荷スイッチング電圧・電流波形

# 1-1. MOS-FETスイッチング時間の定義 Definition of MOS-FET switching time

# 1) td(on): ターンオン遅延時間

td(on): Turn on delay time

通常、縦形MOS-FETではオン抵抗を小さくするためゲート電極の面積は広くなり、それに伴って、入力容量Cissも大きくなる。波形からもわかるようにtd(on)は、ゲートのしきい値電圧Vthまで上昇するまでの充電時間である。従って、ゲート抵抗Rgによって大きく変化する

Normally, in order to make the on resistance of MOS-FET smaller, the area of gate electrode will become bigger. Accordingly, the input capacitance Ciss will also become bigger. As understood from the waveform, td(on) is the time required to reach the gate threshold value Vth. However, it will vary largely according to gate resistance Rg.

### 2) tr:立ち上がり時間

#### tr: Rise time

出力パルスの最大振幅の10%から90%まで増加するのに要する時間。 出力電圧の場合は90%から10%で、電流の場合は10%から90%である。

Rise time is defined as the time required for the output pulse to reach from 10% to 90% of the maximum width. In case of output voltage, it will be from 90% to 10%, and in case of current, it will be 10% to 90%.

## 3) td(off): ターンオフ遅延時間

td(off): Turn off delay time

入力波形 (Vg) の90%から出力電流波形が90%に下降するまで、または、出力電圧波形が10%に上昇するまでの時間で、入力の駆動電圧を引き下げるのに要する放電時間である。入力VG電圧、入力抵抗Rg、入力容量Cissに影響されるため、入力VG電圧は必要以上に高くしないようにして測定する。

It is the time required from the 90% of input (VG) waveform till the current waveform is fallen to 90%. Or, with the time required for the output waveform to rise to 10%, the time necessary to drop the input driving voltage. As it influences the input VG voltage, input resistance Rg, input capacitance Ciss, it is necessary to perform the measurements such that input VG voltage will not be rised more than necessary.

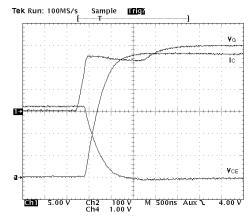

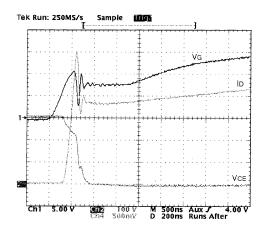

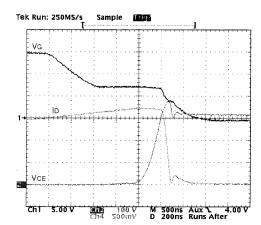

fig-3 R負荷スイッチングON時の波形

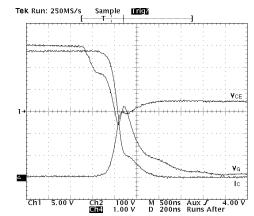

fig-4 R負荷スイッチングOFF時の波形

# スイッチングタイム測定/Switching Time Test

### 4) tf:下降時間

Fall time

出力パルスの最大振幅の90%から10%に下降するまでに要する時間。出力電圧の場合は、10%から90%で、電流の場合は90%から10%である。

The time required for the output pulse to fall from 90% to 10% of the maximum width. In case pf output voltage, it is from 10% to 90% and in case of current, 90% to 10%.

fig-5 L負荷スイッチング基本測定回路

fig-6 L負荷スイッチング電圧・電流波形

### 2. 誘導負荷スイッチング

Inductive Load Switching

fig-5とfig-6にL負荷スイッチング時の各部の基本測定回路と電圧、 電流波形を示す。

Fig-5 and 6 indicate the fundamental measurement circuit, voltage and current waveform during the Inductive load switching.

パワーMOS-FETは多数キャリアデバイスであるため、バイポーラトランジスタのような少数キャリアの蓄積による遅れ時間がなく、きわめて速いスイッチング特性を持っている。またIGBTのスイッチング時間の定義はMOS-FETと同様である。ただし、ターンオン時間がゲート抵抗により大きく変化する点はMOS-FETの特性と同じだが、ターンオフはテイル電流というIGBT特有の動作を示す。

As Power MOS-FET is considered as a majority carrier device, unlike the bipolar transistor which has the accumulation of minority carrier, the delay time does not exist, and has a faster switching characteristics. Again, the definition of IGBT switching time is same as MOS-FET's. However, characteristics of the turn-on time changing greatly according to the gate resistance, is same as MOS-FET. Turn-off indicates the typical operation of IGBT, which is called as tail current.

fig-7 L負荷スイッチングON時の波形

fig-8 L負荷スイッチングOFF時の波形