## 技術情報 TECHNICAL INFORMATION

## di/dt測定/di/dt Test

PN接合ダイオードまたは金属とN形半導体を接触させたショットキーバリアダイオード等は、整流作用を持っている。

2極の接合面であるアノードとカソード間には空乏層による接合容量があり、ダイオードの理想的動きを阻害している。

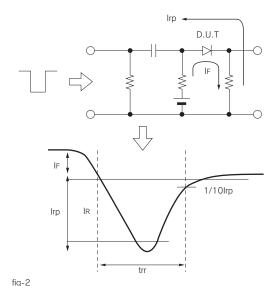

ダイオードに順方向電流IFが流れている時、このダイオードに逆方向電圧 (VR) を印加すると、理想的にはfig-1の様にIF電流が停止するだけであるが、実際はfig-2の様にPN接合の近傍に小数キャリアが残っている間、逆方向であるにも関わらず大きな逆電流 (IR) が流れる。電流の零クロス点からIrpの10%に戻るまでの時間を逆回復時間(trr=Reverse Recovery Time)と言い、ダイオードのスイッチング特性として小さいことが望まれる。また、Trrが大きい場合は使用条件次第では破壊の要因ともなる。

The PN junction diodes or Schottky barrier diodes having the metallic and N-type semiconductor etc, have the characteristics of rectifying action.

In between the anode and cathode of the 2-terminal junction, and according to the depletion layer, it consists of junction capacitance, which violates the ideal working of the diode.

When the forward current IF is flowing in the forward direction, if voltage (VR) is applied in the reverse direction, ideally it will be as per fig-1, and the IF current will be stopped. But, in actuality, as per fig-2, there will be minority carriers. Irrespective of the reverse direction, as long as these carriers exist, a large reverse current (IR) flows. The time from the zero cross point of the current till it returns to 10% of the Irp, is called as the Reverse Recovery Time (Trr), and is considered as small, as far as the diode switching characteristics is considered. Further, in case Trr is long, it may become the reasons for the damage, depending upon the operating conditions.

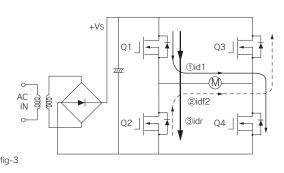

fig-3はパワーMOS-FETをブリッジ構成にしたモーターコントロールの基本回路である。

The fig-3 is the basic circuit for the motor control, for the bridge

fig-1 理想ダイオード

configuration of the power MOS-FET.

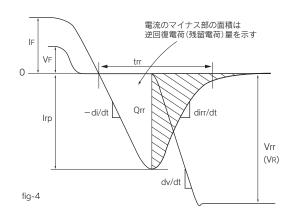

上下交互にON/OFFを繰り返し、そのON/OFF時間を変化させることによりモーターの速度をコントロールする。POWER MOS-FET のほとんどが二重拡散で、構造上ソースードレイン間にダイオードが 等価的に内蔵されているが、トランジスタ、IGBTを使用するときは コレクターエミッタ間にフライホイールダイオードを取り付けなければならない。Q1ーQ4とQ2ーQ3がペアでチョッピングしモーターを コントロールし、Q1ーQ4がオンすると電流id1が流れる。Q1ーQ4がオフしid1が流れなくなると、モーターのインダクタンスに蓄積されたエネルギーにより回生電流id2がQ2の内部ダイオードを通して流れる。この状態でQ1ーQ4がオンすると、Q2の内部ダイオードは逆回復 時間(trr)の導通状態となり、過大な逆電流(リカバリー電流)idrが流れる(Q1とQ2の短絡状態)と同時に+Vs電圧がQ2のダイオードに逆電圧(VR)として印加され、瞬間的にfig-4の斜線部での逆電圧 (VR)と逆電流(IR)の積(VR×IR)という多大なエネルギーがQ2のダイオードに加わり破壊することがある。

この現象はQ2のダイオードへの逆電流IRの傾き(di/dt)が急なほどIrpも大きくなり破壊しやすくなることから、di/dt破壊と言われることもある。

The ON/OFF is repeated consequently up and down. By changing the ON/OFF time, the motor speed is controlled. The power MOSFET is almost with double diffusion, and as per the configuration, diode is built-in between source and drain. When transistor and IGBT are adapted, it is required to attach the flywheel diode. Q1-Q4 and Q2-Q3 are chopped in pair and controls the motor. When Q1-Q4 is ON, current id1 flows. If id1 is stopped by putting Q1-Q4 to OFF, due to the energy stored in the inductance of the motor, the regeneration current id2 flows through the inner diode of Q2. With this condition, if Q1-Q4 is made ON, the reverse recovery time (Trr) of the inner diode of Q2 becomes conducting state, and a excess reverse current (recovery current), idr (in the shorted condition of Q1 & Q2) flows.

## di/dt測定/di/dt Test

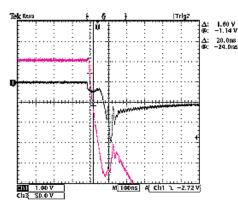

fig-5 di/dt破壊波形

At the same time, the +Vs (supply voltage) is applied to the diode of Q2, as the reverse voltage (VR). Instantaneously as per fig-4, in the shaded area, it results in high energy, VR×IR, with the reverse current (IR) and reverse voltage (VR). This energy is applied to the diode of Q2, resulting in the damage.

This phenomenon becomes severe, when di/dt of the reverse current IR of the diode of Q2 is quick, which makes Irp larger, resulting in the damage. This may also be called as the di/dt damage.

## di/dt測定おけるdi/dtの傾き

Tilt of di/dt in the measurement of di/dt

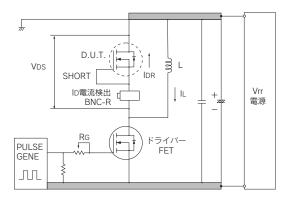

di/dt測定の基本測定回路をfig-6に示す。di/dtの傾きは、ドライバーFET、被測定素子、回路インダクタンス等により大きく値が変わる。また、テスターのヘッドボックス測定においても、テストソケットやテスター内部配線等により約150nH前後の浮遊インダクタンスができてしまう。

測子ケーブル10cmを100nHとし、回路インダクタンスのみで、ほかのドライバーFET等は最良として計算するとfig-7のようになる。

The fundamental measurement circuit for the di/dt measurement is as per fig-6. The tilt in di/dt is greatly changed according to the driver FET, DUT, circuit inductance etc. Further, for the measurement using tester head box, it may create a residual inductance of the order of 150nH due to the internal wiring of the tester and test socket.

If the measurement cable of 10cm is considered as 100nH, fig-7 indicates the calculation for the driver FET, based only on the circuit inductance.

| 測定環境<br>Vrr | ヘッドボックス<br>(150nH) | ヘッドボックス<br>+測子ケーブル<br>10cm<br>(250nH) | ヘッドボックス<br>+測子ケーブル<br>20cm<br>(350nH) |

|-------------|--------------------|---------------------------------------|---------------------------------------|

| Vrr=100V    | 660A/μS            | 400A/μS                               | 280A/μS                               |

| Vrr=200V    | 1300A/μS           | 800A/μS                               | 570A/μS                               |

| Vrr=300V    | 2000A/μS           | 1200A/μS                              | 850A/μS                               |

fig-7 測子ケーブル長と最大di/dtの目安

fig-6 基本測定回路

di/dt試験の必要性

The need of the di/dt test

ダイオードは電流に強く、短時間なら少々の無理をしても壊れることはない、と思うのが多くの技術者の感覚だろう。しかし、この di/dt破壊については知っておく必要がある。なぜなら、di/dt破壊は 高温 (80℃以上) になると発生しやすく、di/dt耐量はカタログ上の 静特性データからは読み取ることはできないからだ。MOS-FET使用の機器で設計上は問題がないにもかかわらず、使用中にMOS-FETの 破壊が発生する場合などはdi/dt破壊を考える必要がある。

製品が小型化し、様々な環境のもとで使用される半導体にとって、 di/dt試験は重要な項目といえる。

Most engineers might think that diodes are resistant to current and will not be broken by a little overwork for a short time. However, it is necessary to know about this di/dt damage. It is because di/dt damage is likely to occur in high-temperature environment, and di/dt strength is unable to be grasped from static characteristic data shown on catalogs. If damage of MOS-FET occurs even if there is no design defect in apparatuses using MOS-FETs, di/dt damage should be considered as a cause.

Miniaturization of products has been improved. The di/dt test is a significant item for semiconductors used in various environments.